基于FPGA的数字电视信号发生器的设计与实现(1)

日期:2010-4-7 10:18:40 点击:

来源:中国工控网

作者:

来源:中国工控网

作者:

点击【 大 中 小 】放大字体.

电视信号的数字化使得数字电视设备越来越受到广大电子消费者的青睐,如何选择自己理想的数字电视产品,也成了消费者关心的问题,评价、测试电视系统与设备运行的质量状况成为广播电视行业所关注的热点。

而数字电视信号发生器能提供可视的测试图像信号,直观、快捷的测试方法,因此,数字电视信号发生器成为目前电子设计的热门研究课题,他在数字电视节目制作播出、科研、生产以及售后服务过程中起着不可或缺的作用。本文设计了一种基于FPGA的数字电视信号友生器,该信号发生器以一种单芯片多配置的方案,针对系统各部分功能特性和性能进行选片没计,并利用FPGA内部存储资源来生成各种测试信号的图像。

1 数字电视信号发生器的功能与原理

1.1 系统功能

数字电视信号发生系统的主要任务是产生符合SMPTE274M系统标准的18种数字信号测试图像,YPbPr,RGB两种视频输出接口符合ITU-R BT.1120-2/GY/T157-2000演播室高清晰度数字视频信号接口标准。本系统的核心是图像信号的编码发生单元FPGA,采取单芯片多配置方案可使18种图像信号方便地进行配置与加密。人机界面由单片机控制,可快速地进行图像切换和格式转换。在普通电源接入下,系统需生成支持 SMPTE274M系统标准中的1080I 60 Hz,1080I 50 Hz,1080P 60 Hz、1080P 50 Hz四种标准格式的18种高清晰度电视通用测试图像的数字输出信号和模拟 输出信号,其标准测试信号的数码发生内核基于FPGA平台实现。在此基础上,本系统提供了一个人工可控功能,即用户可根据按键,对以上4种标准的18种测试图案进行切换控制。考虑到输出信号的实用性,输出的模拟测试信号和数字测试信号都必须满足相应的接口标准。为满足以上约束条件,系统功能设计如图1所示。

1.2信号产生的原理

数字电视也是彩色电视(只是信号的表示形式及信号的处理方法与模拟电视有所不同),因此在考虑数字电视测试信号发生器包含哪些(测试信号)内容时,本文根据彩色电视的基本特点,首先应考虑包含一般彩色电视广播测试图的基本内容,例如观察显示设备扫描非线性失真和几何失真的棋盘信号和圆信号,观察图像清晰度和分辨率的多波群或扫频信号,观察亮度非线性失真情况以及显示器 白平衡调整是否正确的灰度级(或阶梯波)信号,观察彩色重现是否正确的彩条信号等;另外还考虑增加了在视频测量中最常用的2T脉冲信号、彩色多波群信号和彩色阶梯波信号,以及更为直观的斜波信号等,以便全面地观察和评价彩色电视系统或设备的基本质量。

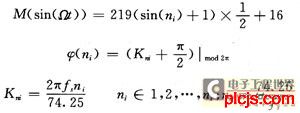

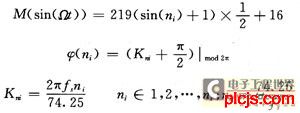

以多波群测试信号为例,他包含了亮度多波群信号和色度多波群信号,信号在任何瞬间的值可用数字硬件中的数代表。对于亮度多波群信号,根据1125/50高清析度电视亮度信号采样频率(74.25 MHz),为避免相位跳变,多波群测试信号各组应含整个采样周期,其频率自左向右各组正弦波的频率(fs)可分别取4.125 MHz,6.187 5 MHz,7.425 MHz,10.6 MHz,14.85 MHz,18.56 MHz;对于色度多波群信号,根据数字电视色差信号采样频率(370 125 MHz)的要求,其频率自左向右各组正弦波的频率(fs)可分别取2.063 MHz,3.094 MHz,3.713 MHz,5.3 MHz,7.425 MHz,9.28 MHz;每组320个取样点,其方程为:

2 数字电视信号发生器的FPGA设计

2.1 FPGA设计原理

FPGA是整个数字电视测试信号发生器系统的核心,各种测试信号编码都在这一部分实现。本系统选用的FPGA是XILINX公司Vertex-E系列的 XCV300E,开发工具为XILINX公司的ISE 6.0,所有测试信号编码均采用Vetilog硬件描述语言编程实现。FPGA设计原理如图2所示。

所有测试信号的编码均基于图像的行/列坐标而产生,其行坐标和列坐标分别为像素计数器和行计数器根据全局时钟上升沿进行计数所得数值。行域信号生成模块对行计数器输出的值进行阈值划分,将测试图像按行划分为不同的区域,称为行域。在不同的行域中,根据像素计数器值进行不同的像素区域划分,将测试图像进一步划分为相对独立的信号编码区域,每个区域对应一个标志信号。此时,行/列坐标与信号编码区域一一对应,称当前输出信号所在行/列所对应的信号编码区域为当前域,其标志信号为当前域标志信号。最后,根据当前域标志信号对测试信号的定时基准码、有效区域等信号进行编码,由测试图案编码模块输出全图像信号数字视频分量的码值。

2.2 FPGA设计总体结构

2.2.1 图像信号产生单元

该模块是系统工作的核心,如图3所示,他由XILINX公司生产的XCV300E组成,是单芯片多配置方式中的主芯片,可提供支持SMPTE274M 1080I 60 Hz/1080I 50 Hz格式的18种高清电视通用测试图,如综合测试卡信号、SMPTE219-2002测试图、SMPTE 198-1998场检测图等。主芯片根据控制模块输出的图案/格式选择信号,选择不同的配置程序,输出相应测试图的数字Y、Cb/Cr信号码值,以及相关的同步/消隐控制信号。

2.2.2 图像信号配置与加密单元

该模块由8片配置芯片XCF02S与1片XC95144XL组成,是成功实现单芯片多配置方案的关键模块。配置程序选择连接开关即根据控制模块输出的5 b配置芯片选择信号,选择相应测试图案的配置芯片PROM的系统可编程JTAG连线与主芯片对应引脚相连接。

WWW_PLC※JS_COM-PLC-技.术_网(可编程控※制器技术门户)

而数字电视信号发生器能提供可视的测试图像信号,直观、快捷的测试方法,因此,数字电视信号发生器成为目前电子设计的热门研究课题,他在数字电视节目制作播出、科研、生产以及售后服务过程中起着不可或缺的作用。本文设计了一种基于FPGA的数字电视信号友生器,该信号发生器以一种单芯片多配置的方案,针对系统各部分功能特性和性能进行选片没计,并利用FPGA内部存储资源来生成各种测试信号的图像。

WWW_P※LCJS_COM-PLC-)技.术_网

1 数字电视信号发生器的功能与原理

WWW_PLC※JS_COM-PmLC-技.术_网

1.1 系统功能

WWW_PLCJS_COM-PLC-技.术_网

数字电视信号发生系统的主要任务是产生符合SMPTE274M系统标准的18种数字信号测试图像,YPbPr,RGB两种视频输出接口符合ITU-R BT.1120-2/GY/T157-2000演播室高清晰度数字视频信号接口标准。本系统的核心是图像信号的编码发生单元FPGA,采取单芯片多配置方案可使18种图像信号方便地进行配置与加密。人机界面由单片机控制,可快速地进行图像切换和格式转换。在普通电源接入下,系统需生成支持 SMPTE274M系统标准中的1080I 60 Hz,1080I 50 Hz,1080P 60 Hz、1080P 50 Hz四种标准格式的18种高清晰度电视通用测试图像的数字输出信号和

WWW_PLCJS@_COM%-PLC-技.术_网

WWW_PL※CJS_COM-PLC-技.术_网

1.2信号产生的原理

WWW_PLC※JS_COM-PLC-技.术_网(可编程控※制器技术门户)

数字电视也是彩色电视(只是信号的表示形式及信号的处理方法与模拟电视有所不同),因此在考虑数字电视测试信号发生器包含哪些(测试信号)内容时,本文根据彩色电视的基本特点,首先应考虑包含一般彩色电视广播测试图的基本内容,例如观察显示设备扫描非线性失真和几何失真的棋盘信号和圆信号,观察图像清晰度和分辨率的多波群或扫频信号,观察亮度非线性失真情况以及

WWW※PLCJS_COM-PL#C-技.术_网(可编※程控※制器技术门户)

以多波群测试信号为例,他包含了亮度多波群信号和色度多波群信号,信号在任何瞬间的值可用数字硬件中的数代表。对于亮度多波群信号,根据1125/50高清析度电视亮度信号采样频率(74.25 MHz),为避免相位跳变,多波群测试信号各组应含整个采样周期,其频率自左向右各组正弦波的频率(fs)可分别取4.125 MHz,6.187 5 MHz,7.425 MHz,10.6 MHz,14.85 MHz,18.56 MHz;对于色度多波群信号,根据数字电视色差信号采样频率(370 125 MHz)的要求,其频率自左向右各组正弦波的频率(fs)可分别取2.063 MHz,3.094 MHz,3.713 MHz,5.3 MHz,7.425 MHz,9.28 MHz;每组320个取样点,其方程为:

WWW_PLCJS@_COM%-PLC-技.术_网

W1WW_P4LCJS_COM-PLC-技.术_网

2 数字电视信号发生器的FPGA设计

WW.W_PLC※JS_C,OM-PL,C-技.术_网

2.1 FPGA设计原理

P.L.C.技.术.网——可编程控制器技术门户

FPGA是整个数字电视测试信号发生器系统的核心,各种测试信号编码都在这一部分实现。本系统选用的FPGA是XILINX公司Vertex-E系列的 XCV300E,开发工具为XILINX公司的ISE 6.0,所有测试信号编码均采用Vetilog硬件描述语言编程实现。FPGA设计原理如图2所示。

WWW_PLCJS@_COM%-PLC-技.术_网

WWW_PLCJS※COM-PLC-技×术_网(可编程控※制器技术门户)

所有测试信号的编码均基于图像的行/列坐标而产生,其行坐标和列坐标分别为像素计数器和行计数器根据全局时钟上升沿进行计数所得数值。行域信号生成模块对行计数器输出的值进行阈值划分,将测试图像按行划分为不同的区域,称为行域。在不同的行域中,根据像素计数器值进行不同的像素区域划分,将测试图像进一步划分为相对独立的信号编码区域,每个区域对应一个标志信号。此时,行/列坐标与信号编码区域一一对应,称当前输出信号所在行/列所对应的信号编码区域为当前域,其标志信号为当前域标志信号。最后,根据当前域标志信号对测试信号的定时基准码、有效区域等信号进行编码,由测试图案编码模块输出全图像信号数字视频分量的码值。

WWW.PLCJS.COM——可编程控制器技术门户

2.2 FPGA设计总体结构

W1WW_P4LCJS_COM-PLC-技.术_网

2.2.1 图像信号产生单元

——可——编——程——控-制-器-技——术——门——户

该模块是系统工作的核心,如图3所示,他由XILINX公司生产的XCV300E组成,是单芯片多配置方式中的主芯片,可提供支持SMPTE274M 1080I 60 Hz/1080I 50 Hz格式的18种高清电视通用测试图,如综合测试卡信号、SMPTE219-2002测试图、SMPTE 198-1998场检测图等。主芯片根据控制模块输出的图案/格式选择信号,选择不同的配置程序,输出相应测试图的数字Y、Cb/Cr信号码值,以及相关的同步/消隐控制信号。

WWcW_PLCJS_COM-PLC-技.术_网

WWW.PLCJS.COM——可编程控制器技术门户

2.2.2 图像信号配置与加密单元

WW.W_PLCJS_COM-PLC-技.术_网

该模块由8片配置芯片XCF02S与1片XC95144XL组成,是成功实现单芯片多配置方案的关键模块。配置程序选择连接开关即根据控制模块输出的5 b配置芯片选择信号,选择相应测试图案的配置芯片PROM的系统可编程JTAG连线与主芯片对应引脚相连接。

WWW_PLCJS_COM-PLC-技.术_网

上一篇: 基于FPGA的数字电视信号发生器的设计与实现(2)下一篇: 没有了

评论内容

载入中...

载入中...

P

L

C

技

术

网

|

可

编

程

控

制

器

技

术

门

户

|

十

万

P

L

C

工

程

师

的

共

同

选

择

!

L

C

技

术

网

|

可

编

程

控

制

器

技

术

门

户

|

十

万

P

L

C

工

程

师

的

共

同

选

择

!

·最新招聘信息

·最新求职信息

·推荐产品

·推荐厂商

·栏目热门排行

·站内热门排行