点击: 作者:未知

1 引言

在数字通信系统中,原始的模拟信号经量化编码转变成二进制码流(即数字基带信号)后,必须经过调制后才适合于传输。fsk(移频键控)即为一种常用的数字调制方式,它是利用载波频率的变化来传递数字信息,所以也可以称为数字调频。

若用2种载波频率分别代表二进制码流所含的两种基本码元,此时的数字调频即为2fsk调制。若2个载频由不同的独立振荡器提供,他们之间相位互不相关,就称为相位离散的数字调频信号,若两个频率由同一振荡信号源提供,只是对其中的载频进行分频,这样产生的两个载频就是相位连续的数字调频信号。

2 分频法实现fsk调制器的方案

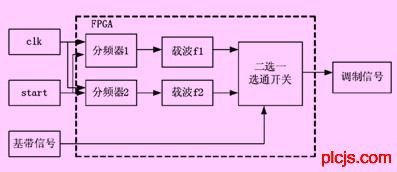

键控法也常常利用数字基带信号去控制可变分频器的分频比来改变输出载波频率,从而实现fsk调制。fsk调制方框图如图1所示。

图1 fsk调制方框图

fsk调制的核心部分包括分频器、二选一选通开关等。图1中的两个分频器分别产生两路数字载波信号;二选一选通开关的作用是:以基带信号作为控制信号,当基带信号为“0”,选通载波f1;当基带信号为“1”时,选通载波f2。从选通开关输出的信号就是数字fsk信号。图中没有包含模拟电路部分,调制信号为数字信号。

采用可变分频器产生的fsk信号相位通常是连续的,因此在基带信息变化时,fsk信号会出现过渡频率。为减小过渡时间,可变分频器应工作于较高的频率,而在可变分频器后再插入固定分频器,使输出频率满足fsk信号要求的频率。

3 用fpga实现fsk信号的调制及仿真

3.1 vhdl建模符号

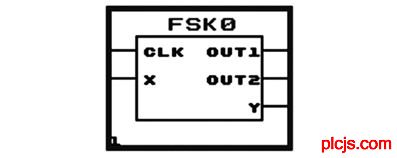

fsk调制电路的vhdl建模符号如图2所示。

图2 fsk调制电路的vhdl建模符号

3.2 vhdl程序设计

分频法fsk调制器的源代码如下:

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fsk0 is

port(clk :in std_logic;

x :in std_logic;

out1 :buffer std_logic;

out2 :buffer std_logic;

y :out std_logic);

end fsk0;

architecture behav of fsk0 is

signal division1,division2,division3,division4 :std_logic:=0;

signal temp1,temp2,temp3,temp4:integer range 0 to 20;

begin

a1:process(clk)

begin

if clkevent and clk=1 then

temp1 <=temp1+1;

if temp1=7 then division1<=1;

elsif temp1=14 then division1<=0;

temp1<=0;

end if;

end if;

end process a1;

a2:process(clk)

begin

if clkevent and clk=0 then

temp2<=temp2+1;

if temp2=7 then division2<=1;

elsif temp2=14 then division2<=0;

temp2<=0;

end if;

end if;

end process a2;

a3:process(division1,division2)

begin

out1<=division2 or division1;

end process a3;

a4:process(clk)

begin

if clkevent and clk=1 then temp3 <=temp3+1;

if temp3=8 then division3<=1;

elsif temp3=16 then division3<=0;

temp3<=0;

end if;

end if;

end process a4;

a5:process(clk)

begin

if clkevent and clk=0 then temp4<=temp4+1;

if temp4=8 then division4<=1;

elsif temp4=16 then division4<=0;

temp4<=0;

end if;

end if;

end process a5;

a6:process(division3,division4)

begin

out2<=division3 or division4;

end process a6;

a7:process(x,out1,out2)

begin

if x=1 then y<=out1;

else y<=out2;

end if;

end process a7;

end behav;

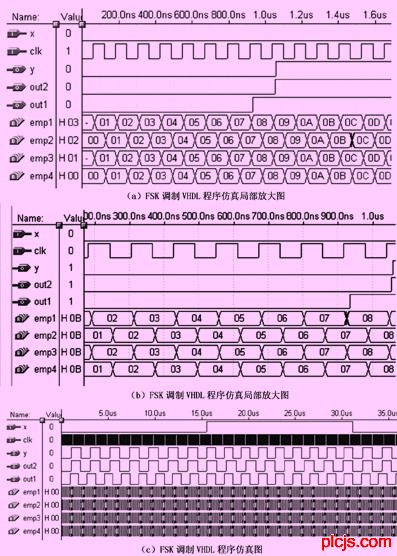

3.3 仿真结果

程序仿真图如图3所示。

图3 程序仿真图

3.4 引脚锁定

前面所做的只是逻辑功能的软件模拟仿真,即使模拟仿真、时序分析都达到设计要求,这只是理论上的结果,实际硬件的执行与软件模拟不一定完全一样,最后必须做硬件的验证。在做硬件验证时,各个输入、输出信号必须锁定到具体芯片的脚上,才能将外部信号加进来,将输出信号接出去,根据外部电路设计,将设计中各个输入、输出信号锁定到芯片的管脚上。选择菜单[assign]下的[pin/location/chip...]功能,出现如图4所示的信号与芯片管脚锁定的对话框,在“node name”框内填入需要输入、输出的信号名,在“pin type”框内显示出该信号的输入、输出类型,在“pin”复选框内选择芯片的管脚,按右下角的“add”按钮将信号与管脚的锁定关系加入“existing pin / location / chip assignments”框内,当所有的信号都加入后,按“ok”确认退出。注意:如果你的设计中有时钟信号、复位信号、输出允许信号等可以全局使用的信号,编译器会自动将这些信号分配到芯片的相应全局信号管脚,如果你锁定的管脚不是全局信号脚,在编译综合时,系统会提示有错,解决的方法是,选择[assign]菜单下的[global project synthesis] 功能,在弹出的对话框的“automatic global”栏内,去掉所使用全局信号前的选中勾,使其不会被自动分配。按“ok”钮确认退出。

L

C

技

术

网

|

可

编

程

控

制

器

技

术

门

户

|

十

万

P

L

C

工

程

师

的

共

同

选

择

!