利用EDA工具提高系统级芯片测试的效率

日期:2010-1-14 10:42:24 点击:

来源:中国工控网

作者:

来源:中国工控网

作者:

点击【 大 中 小 】放大字体.

高度复杂的SoC设计正面临着高可靠性、高质量、低成本以及更短的产品上市周期等日益严峻的挑战。可测性设计通过提高电路的可测试性,从而保证芯片的高质量生产和制造。借助于EDA技术,可以实现可测试性设计的自动化,提高电路开发工作效率,并获得高质量的测试向量,从而提高测试质量、低测试成本。

半导体工艺的进步以摩尔定率的速度推动着集成电路产业的发展。随着芯片的工艺尺寸越来越细,集成度越来越高,半导体工艺加工中可能引入越来越多的各种失效。传统的利用功能仿真向量进行生产制造芯片的后期测试,虽然有的工程师认为由于充分测试过电路的功能,所以功能测试向量应该可以满足市场对产品质量的需求,然而实际上功能测试向量还很不完备,亚微米、深亚微米制造工艺条件下,功能测试向量所能达到的测试覆盖率只有50%到 60%左右,测试的质量得不到充分保证;另外功能测试向量的产生和运行都十分昂贵;与此同时功能测试向量还不便于失效器件的故障诊断。

可测试性设计的内容与EDA技术

半导体工艺中可能引入各种失效,材料的缺陷以及工艺偏差都可能导致芯片中电路连接的短路、断路以及器件结间穿通等问题。而这样的物理失效必然导致电路功能或者性能方面的故障,对这些电学故障进行逻辑行为抽象就称为故障模型。例如,最常用的一种类型的电学故障可以抽象为单元中的信号状态被锁定在逻辑“0”或者逻辑“1”上(SA0或者SA1),这种类型物理失效的抽象模式被称为“Stuck-at”的故障模型;对于深亚微米制造工艺的芯片,其高性能的测试中还必须结合多种实速(at-speed)故障模型,包括跃迁故障模型、路径延时故障模型和IDDQ故障模型等。

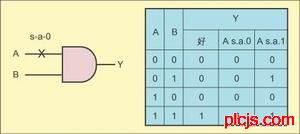

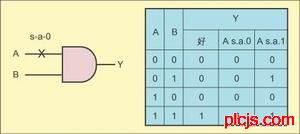

Stuck-at故障模型示例如图1所示,其测试向量及测试结果的判断如该真值表所示。通常情况下,多数工艺失效问题都可以通过利用stuck-at故障模型测试到。

图1:Stuck-at故障测试。

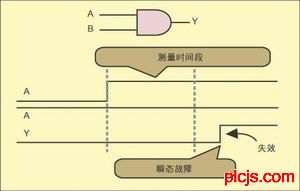

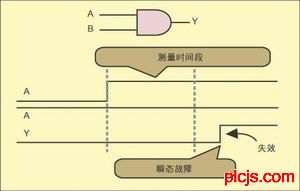

跃迁故障模型包括慢上升(Slow-to-Rise)和慢下降(Slow-to-Fall)两种类型。我们以慢上升故障模型为例来说明跃迁故障模型的测试。如图2所示,观测窗口是电路正常工作所允许的最大跃迁延迟时间,测试时如果在观测窗口时间段内扑获不到期望的输出,则认为被测试节点存在跃迁故障。

图2:跃迁故障测试。

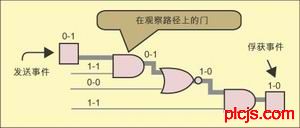

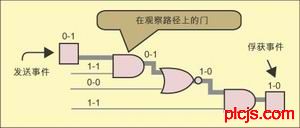

路径延时故障模型与跃迁故障模型类似,不同的是利用路径延时故障模型测试的电路的某一路径的集中延时情况。如图3所示,路径延时故障模型测试的对象是一条时序路径,通过对路径的输入端赋值进行触发,然后在特定的观测时间窗口内、在路径输出端捕获期望输出。

图3:路径延时故障测试。

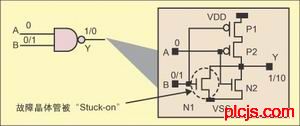

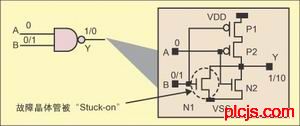

IDDQ故障模型利用在电路稳态情况下观测电源的静态漏电流的变化情况达到测试电路失效故障的目的。如图4所示,如果电路的B节点存在SA1故障,晶体管N1处于常开启状态,测试时会发现改变B节点的输入激励,电源的静态漏电流的变化不大。

图4:IDDQ故障模型测试。

可测性设计(DFT)就是确保设计的电路具备更高的可测试性并且自动产生高质量的测试向量集;其目的就是为了确保ASIC/SOC芯片在生产制造之后,通过测试的产品都能够正确无误地工作。可测性设计的内容主要包括:1. 测试综合:芯片设计过程中DFT在设计中自动插入测试结构,确保生产加工后的芯片易于测试。2. ATPG:利用EDA工具自动产生可以在ATE上运行的测试向量,利用EDA工具自动诊断导致元器件失效的故障产生的原因。3. BIST:利用EDA工具自动生成被测电路的测试用IP,完成测试序列生成和输出响应分析两个任务,通过分析被测电路的响应输出,判断被测电路是否有故障。

如图5所示是DFT解决方案:对全扫描逻辑电路的测试,设计者可以选用Fastscan,对部分扫描逻辑电路的测试,设计者可以选用Flextest,对IP或宏模块的内建自测试,设计者也可以选用LBISTArchitect。对Memory的测试,设计者可以选用 MBISTArchitect,也可以选用fastscan的子模块功能Macrotest。采用边界扫描电路的设计,设计者可以选用 BSDArchitect。

测试综合完成自动插入全扫描或部分扫描的测试逻辑,大大增强了IC和ASIC设计的可测试性。它在设计过程的早期阶段进行可测性分析,在测试向量生成和扫描自动综合之前发现并修改违反测试设计规则的问题,尽可能提高ATPG的效率并缩短测试开发的周期。

WWW_PLCJS※COM-PLC-技.术_网(可※编程控※制器技术门户)

高度复杂的SoC设计正面临着高可靠性、高质量、低成本以及更短的产品上市周期等日益严峻的挑战。可测性设计通过提高电路的可测试性,从而保证芯片的高质量生产和制造。借助于EDA技术,可以实现可测试性设计的自动化,提高电路开发工作效率,并获得高质量的测试向量,从而提高测试质量、低测试成本。

WWW_P※LCJS_CO※M-PLC-技-.术_网

半导体工艺的进步以摩尔定率的速度推动着集成电路产业的发展。随着芯片的工艺尺寸越来越细,集成度越来越高,半导体工艺加工中可能引入越来越多的各种失效。传统的利用功能仿真向量进行生产制造芯片的后期测试,虽然有的工程师认为由于充分测试过电路的功能,所以功能测试向量应该可以满足市场对产品质量的需求,然而实际上功能测试向量还很不完备,亚微米、深亚微米制造工艺条件下,功能测试向量所能达到的测试覆盖率只有50%到 60%左右,测试的质量得不到充分保证;另外功能测试向量的产生和运行都十分昂贵;与此同时功能测试向量还不便于失效器件的故障诊断。

WWW_P※LCJS_COM-PLC-)技.术_网

可测试性设计的内容与EDA技术

WWW_PLCJS※COM-PLC-技×术_网(可编程控※制器技术门户)

半导体工艺中可能引入各种失效,材料的缺陷以及工艺偏差都可能导致芯片中电路连接的短路、断路以及器件结间穿通等问题。而这样的物理失效必然导致电路功能或者性能方面的故障,对这些电学故障进行逻辑行为抽象就称为故障模型。例如,最常用的一种类型的电学故障可以抽象为单元中的信号状态被锁定在逻辑“0”或者逻辑“1”上(SA0或者SA1),这种类型物理失效的抽象模式被称为“Stuck-at”的故障模型;对于深亚微米制造工艺的芯片,其高性能的测试中还必须结合多种实速(at-speed)故障模型,包括跃迁故障模型、路径延时故障模型和IDDQ故障模型等。

WWW_P※LCJS_CO※M-PLC-技-.术_网

WWW_P※LCJS_COM-PLC-)技.术_网

Stuck-at故障模型示例如图1所示,其测试向量及测试结果的判断如该真值表所示。通常情况下,多数工艺失效问题都可以通过利用stuck-at故障模型测试到。

WWW_PLCJS※COM-PLC-技.术_网(可※编程控※制器技术门户)

plcjs.技.术_网

图1:Stuck-at故障测试。

WWW_PLCJS_COM-PLC-技.术_网

跃迁故障模型包括慢上升(Slow-to-Rise)和慢下降(Slow-to-Fall)两种类型。我们以慢上升故障模型为例来说明跃迁故障模型的测试。如图2所示,观测窗口是电路正常工作所允许的最大跃迁延迟时间,测试时如果在观测窗口时间段内扑获不到期望的输出,则认为被测试节点存在跃迁故障。

WWW_PLCJS_COM-PLC-技.术_网

W1WW_P4LCJS_COM-PLC-技.术_网

图2:跃迁故障测试。

WW.W_PLCJS_COM-PLC-技.术_网

路径延时故障模型与跃迁故障模型类似,不同的是利用路径延时故障模型测试的电路的某一路径的集中延时情况。如图3所示,路径延时故障模型测试的对象是一条时序路径,通过对路径的输入端赋值进行触发,然后在特定的观测时间窗口内、在路径输出端捕获期望输出。

WWW_PLCJS_COM-PLC-技.术_网

WWW.PLCJS.COM——可编程控制器技术门户

图3:路径延时故障测试。

WWW_PL※CJS_COM-PLC-技.术_网

IDDQ故障模型利用在电路稳态情况下观测电源的静态漏电流的变化情况达到测试电路失效故障的目的。如图4所示,如果电路的B节点存在SA1故障,晶体管N1处于常开启状态,测试时会发现改变B节点的输入激励,电源的静态漏电流的变化不大。

WWW_PLCJ-S_COM-PLC-技.术_网(可-编程控-制器技术-门户)

WWW_PLC※JS_COM-PmLC-技.术_网

图4:IDDQ故障模型测试。

WWW_PLCJ-S_COM-PLC-技.术_网(可-编程控-制器技术-门户)

可测性设计(DFT)就是确保设计的电路具备更高的可测试性并且自动产生高质量的测试向量集;其目的就是为了确保ASIC/SOC芯片在生产制造之后,通过测试的产品都能够正确无误地工作。可测性设计的内容主要包括:1. 测试综合:芯片设计过程中DFT在设计中自动插入测试结构,确保生产加工后的芯片易于测试。2. ATPG:利用EDA工具自动产生可以在ATE上运行的测试向量,利用EDA工具自动诊断导致元器件失效的故障产生的原因。3. BIST:利用EDA工具自动生成被测电路的测试用IP,完成测试序列生成和输出响应分析两个任务,通过分析被测电路的响应输出,判断被测电路是否有故障。

WWW_PL※CJS_COM-PLC-技.术_网

如图5所示是DFT解决方案:对全扫描逻辑电路的测试,设计者可以选用Fastscan,对部分扫描逻辑电路的测试,设计者可以选用Flextest,对IP或宏模块的内建自测试,设计者也可以选用LBISTArchitect。对Memory的测试,设计者可以选用 MBISTArchitect,也可以选用fastscan的子模块功能Macrotest。采用边界扫描电路的设计,设计者可以选用 BSDArchitect。

W1WW_P4LCJS_COM-PLC-技.术_网

P.L.C.技.术.网——可编程控制器技术门户

测试综合完成自动插入全扫描或部分扫描的测试逻辑,大大增强了IC和ASIC设计的可测试性。它在设计过程的早期阶段进行可测性分析,在测试向量生成和扫描自动综合之前发现并修改违反测试设计规则的问题,尽可能提高ATPG的效率并缩短测试开发的周期。

WWW_PLCJS_COM-PLC-技.术_网

评论内容

载入中...

载入中...

P

L

C

技

术

网

|

可

编

程

控

制

器

技

术

门

户

|

十

万

P

L

C

工

程

师

的

共

同

选

择

!

L

C

技

术

网

|

可

编

程

控

制

器

技

术

门

户

|

十

万

P

L

C

工

程

师

的

共

同

选

择

!

·最新招聘信息

·最新求职信息

·推荐产品

·推荐厂商

·栏目热门排行

·站内热门排行